FPGA芯片的逻辑资源是衡量开发板性能的重要指标,包括逻辑单元(LE)、查找表(LUT)、触发器(FF)、DSP切片和块RAM(BRAM)等,选型时需根据项目需求匹配资源规模。对于入门级项目,如基础逻辑实验、简单控制器设计,选择逻辑单元数量在1万-10万之间的FPGA芯片即可,如XilinxArtix-7系列的xc7a35t芯片,具备35k逻辑单元、50个DSP切片和900KBBRAM,能满足基础开发需求。对于要求高的项目,如AI推理加速、高速数据处理,需选择逻辑单元数量在10万-100万之间的芯片,如XilinxKintex-7系列的xc7k325t芯片,具备326k逻辑单元、1728个DSP切片和BRAM,支持复杂算法的实现。DSP切片数量影响信号处理能力,适合需要大量乘法累加运算的场景;块RAM容量影响数据缓存能力,适合需要存储大量中间数据的项目。选型时需避免资源过剩导致成本浪费,也需防止资源不足无法实现设计功能,可通过前期需求分析和资源估算确定合适的芯片型号。 FPGA 开发板扩展模块支持多传感器采集。黑龙江学习FPGA开发板芯片

FPGA开发板在机器人领域发挥着作用,助力机器人实现更加智能的动作。在工业机器人中,开发板用于处理机器人运动算法,根据预设的路径和任务要求,精确机器人各个关节的运动。通过与电机驱动器通信,开发板向电机发送信号,实现对电机转速、转矩和位置的精确调节,从而保证机器人能够准确地完成各种复杂的操作,如搬运、装配、焊接等任务。在服务机器人中,开发板除了负责运动外,还承担着人机交互和环境感知数据处理的任务。开发板接收来自摄像头、麦克风、超声波传感器等设备采集的环境信息,通过算法对这些信息进行分析和理解,使机器人能够感知周围环境,与人类进行自然交互。例如,服务机器人在遇到障碍物时,开发板根据传感器数据及时调整机器人的运动方向,避免碰撞;在与用户交流时,开发板对语音信号进行处理和识别,理解用户的指令并做出相应的回应,提升机器人的智能化水平和服务质量。黑龙江学习FPGA开发板解决方案FPGA 开发板扩展槽兼容传感器模块接入。

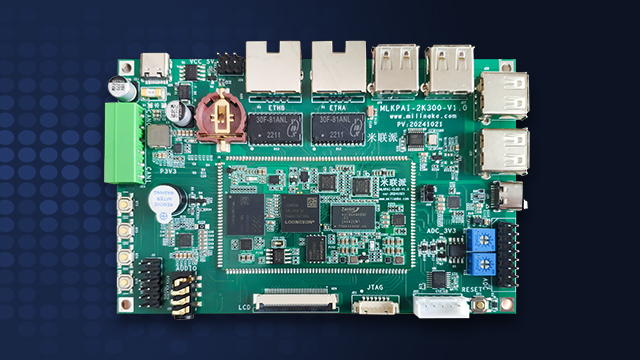

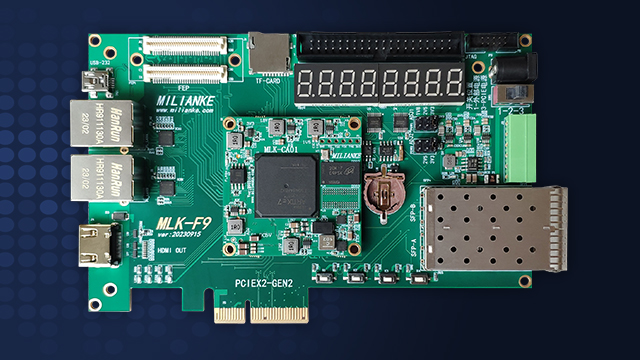

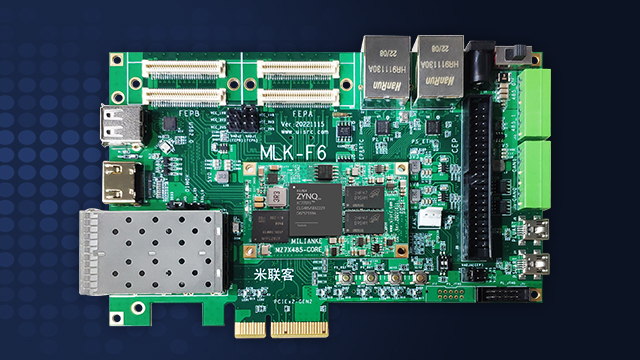

FPGA开发板是电子工程师与爱好者探索硬件世界的重要载体,其硬件架构设计精巧且功能丰富。以常见的XilinxZynq系列开发板为例,这类开发板集成了ARM处理器与FPGA可编程逻辑资源,形成独特的异构架构。ARM处理器部分可运行嵌入式操作系统,用于处理复杂的系统管理任务和软件算法,诸如文件系统管理、网络通信协议栈运行等;而FPGA部分则可根据设计需求灵活构建各类数字电路。开发板上还配备了丰富的存储模块,包括用于程序存储的Flash芯片,能在断电后长久保存系统启动代码与用户程序;以及用于数据缓存的DDR内存,可在运行时存取大量数据。此外,开发板设置多种通信接口,以太网接口方便连接网络进行数据传输与远程调试,USB接口支持多种设备连接,方便数据交互,SPI、I²C等接口则用于连接各类传感器与外设芯片,为开发者搭建复杂硬件系统提供了充足的拓展空间。

科研人员在进行前沿技术研究时,FPGA开发板是重要的工具之一。在人工智能领域,科研人员利用开发板实现神经网络算法的硬件加速,通过编程优化神经网络计算过程,提高计算效率。在生物医学工程(不涉及医疗内容)领域外的相关研究中,如生物传感器信号处理研究,开发板可用于处理生物电信号,分析信号特征。FPGA开发板的灵活性与可编程性,使科研人员能够快速实现新的研究思路与算法,对采集的数据进行实时处理与分析,为各领域前沿技术研究提供实验平台,推动科研工作的进展与创新。FPGA 开发板是硬件学习者的必备设备!

FPGA开发板在金融领域的应用逐渐兴起,为金融科技的发展带来新的机遇。在高频交易系统中,时间就是金钱,对数据处理速度和实时性要求极高。FPGA开发板凭借其高速并行处理能力,能够快速获取金融市场的实时行情数据,如价格、汇率、期货价格等。通过预先编写的交易算法,开发板对这些数据进行实时分析和处理,在极短的时间内做出交易决策,并执行交易指令。与传统的基于CPU的交易系统相比,FPGA开发板能够缩短交易延迟,提高交易效率,帮助金融机构在激烈的市场竞争中抢占先机。同时,开发板的可重构特性使得金融机构能够根据市场变化和交易策略的调整,快速对交易算法进行修改和优化,实现交易系统的灵活升级,更好地适应复杂多变的金融市场环境,提升金融交易的智能化和高效化水平。FPGA 开发板原理图标注信号流向与网络名。湖南开发FPGA开发板板卡设计

FPGA 开发板用户手册详述硬件资源分布。黑龙江学习FPGA开发板芯片

1.FPGA开发板的时钟模块作用时钟信号是FPGA数字逻辑设计的“脉搏”,开发板上的时钟模块通常由晶体振荡器、时钟缓冲器和时钟分配网络组成。晶体振荡器能提供高精度的固定频率信号,常见频率有25MHz、50MHz、100MHz等,部分板卡还会集成可配置的时钟发生器,支持通过软件调整输出频率,满足不同算法对时钟周期的需求。时钟缓冲器可将单一时钟信号复制为多路同步信号,分配给FPGA内部的不同逻辑模块,避免因信号延迟导致的时序偏差。在高速数据处理场景中,如图像处理或通信信号解调,时钟模块的稳定性直接影响数据采样精度和逻辑运算的同步性,因此部分开发板还会加入时钟抖动抑制电路,进一步降低信号噪声。黑龙江学习FPGA开发板芯片