FPGA开发板可通过多种接口连接各类传感器,实现数据采集、处理和存储,适合环境监测、工业检测、医疗设备等场景。常见的传感器包括温湿度传感器(如DHT11、SHT30)、加速度传感器(如ADXL345)、光照传感器(如BH1750)、图像传感器(如OV7670、MT9V034)。在温湿度采集场景中,FPGA通过I2C或单总线接口读取传感器数据,进行滤波处理后,通过UART发送到计算机或显示在OLED屏幕上;在加速度采集场景中,FPGA通过SPI接口读取传感器的三轴加速度数据,实现运动检测或姿态识别;在图像采集场景中,FPGA通过并行接口或MIPI接口接收图像传感器的原始数据,进行预处理(如去噪、裁剪)后,存储到SD卡或通过HDMI显示。传感器数据采集需注意接口时序匹配和数据格式转换,例如不同传感器的I2C通信时序可能存在差异,需在FPGA代码中针对性设计;传感器输出的模拟信号需通过ADC转换为数字信号,再由FPGA处理。部分开发板会提供传感器数据采集的示例代码,简化开发流程,帮助开发者快速实现功能。 FPGA 开发板扩展模块支持多传感器采集。广东使用FPGA开发板工程师

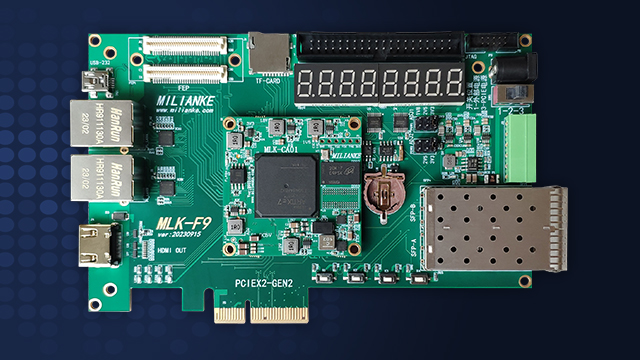

PCIe接口是FPGA开发板与计算机或其他高速设备进行数据交互的重要接口,常见版本包括PCIe2.0、PCIe3.0、PCIe4.0,通道数从x1到x16不等。其优势是高带宽和低延迟,例如PCIex16接口的传输速率可达64GB/s,适合需要高速数据传输的场景。在计算机加速场景中,FPGA开发板可通过PCIe接口连接计算机,作为硬件加速器,加速CPU的计算任务,如视频编码解码、科学计算;在数据采集场景中,可通过PCIe接口接收计算机发送的控制指令,或将采集到的高速数据传输到计算机进行存储和分析。部分FPGA开发板采用PCIe插槽形式,可直接插入计算机主板的PCIe插槽,方便集成;也有开发板采用PCIe转USB接口,通过USB线缆与计算机连接,提升使用灵活性。使用PCIe接口时,需实现PCIe协议栈,部分FPGA厂商提供现成的PCIeIP核,简化协议栈的开发,开发者可专注于应用逻辑设计。 黑龙江开发板FPGA开发板学习步骤FPGA 开发板按键消抖电路保证输入稳定。

FPGA开发板在教育领域扮演着越来越重要的角色,成为数字电路和嵌入式系统教学的重要工具。通过FPGA开发板,学生和学习者可以实践性地理解数字逻辑设计的原理,掌握HDL编程的技巧,并加深对现代电子系统的理解。许多高校和培训机构已经将FPGA开发板纳入课程体系,帮助学生提升实际操作能力和创新能力。此外,FPGA开发板的丰富资源和开源社区也为学习者提供了大量的教程和项目实例,进一步降低了学习门槛,促进了电子工程专业人才的培养。

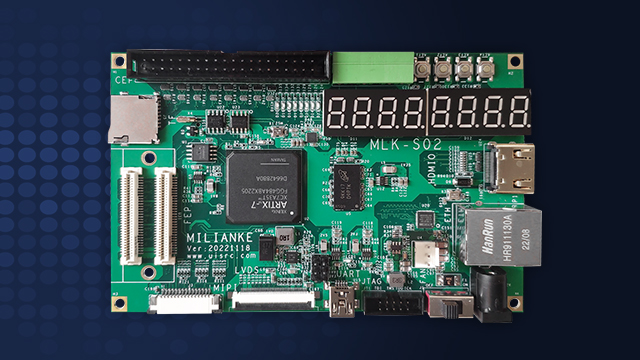

FPGA开发板的成本控制需在满足功能需求的前提下,优化硬件设计和元器件选型,适合教育、中小企业等对成本敏感的场景。成本控制可从以下方面实现:一是选择中低端FPGA芯片,如XilinxArtix-7系列、IntelCycloneIV系列,这类芯片逻辑资源适中,价格亲民,能满足基础开发需求;二是简化外设配置,减少不必要的接口和模块,如保留常用的UART、SPI、LED、按钮,去除HDMI、PCIe接口;三是选用低成本元器件,如采用国产电容电阻、简化封装的连接器,降低硬件成本;四是优化PCB设计,采用双面板或4层板,减少层数,降成本。成本控制需平衡功能与价格,避免过度压缩成本导致性能下降或可靠性问题,例如选用劣质电源模块可能导致供电不稳定,影响FPGA工作;减少必要的测试点可能增加调试难度。部分厂商推出专门的入门级开发板,价格低于100美元,配套基础教程和代码示例,适合学生和初学者学习使用。 FPGA 开发板教程包含错误排查方法指导。

通信系统需要处理大量的高速信号,包括信号调制解调、编码解码、数据转发等,FPGA开发板凭借其高速信号处理能力和灵活的接口,成为通信系统开发的重要工具。在无线通信场景中,FPGA开发板可实现基带信号处理,如OFDM调制解调、卷积码编码解码,支持4G、5G等通信标准;在有线通信场景中,可实现以太网、光纤通信的信号处理,如TCP/IP协议栈加速、光信号的编解码。部分FPGA开发板集成高速串行接口,如10G/25GEthernet、PCIe,支持高速数据传输;还会集成射频前端模块,方便连接天线,实现无线信号的收发。在通信设备研发中,FPGA开发板可作为原型平台,验证新的通信算法或协议,例如测试5GNR(新无线)技术的信号处理性能,或验证卫星通信中的抗干扰算法,确保通信系统的稳定性和可靠性。 FPGA 开发板原理图标注信号流向与网络名。广东使用FPGA开发板工程师

FPGA 开发板示例代码注释清晰便于学习。广东使用FPGA开发板工程师

1.FPGA开发板的时钟模块作用时钟信号是FPGA数字逻辑设计的“脉搏”,开发板上的时钟模块通常由晶体振荡器、时钟缓冲器和时钟分配网络组成。晶体振荡器能提供高精度的固定频率信号,常见频率有25MHz、50MHz、100MHz等,部分板卡还会集成可配置的时钟发生器,支持通过软件调整输出频率,满足不同算法对时钟周期的需求。时钟缓冲器可将单一时钟信号复制为多路同步信号,分配给FPGA内部的不同逻辑模块,避免因信号延迟导致的时序偏差。在高速数据处理场景中,如图像处理或通信信号解调,时钟模块的稳定性直接影响数据采样精度和逻辑运算的同步性,因此部分开发板还会加入时钟抖动抑制电路,进一步降低信号噪声。广东使用FPGA开发板工程师