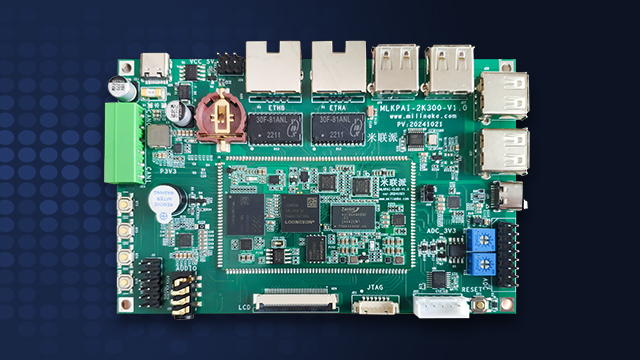

FPGA定制项目之智慧物流包裹分拣识别模块开发某物流企业需定制FPGA包裹分拣识别模块,用于自动化分拣流水线,要求识别包裹面单上的条形码与二维码,识别成功率不低于98%,单包裹处理时间小于1秒,适配流水线每秒2个包裹的传输速度。项目团队选用XilinxArtix-7系列FPGA,其高速图像识别与并行处理能力可满足分拣效率需求。开发过程中,FPGA对接流水线高清相机,接收包裹面单图像后,先进行图像预处理(去模糊、增强对比度),再通过条码识别算法提取编码信息,与物流系统中的订单数据匹配,生成分拣指令发送至机械臂。硬件设计加入图像缓存模块,避免包裹传输过快导致数据丢失;软件层面支持多种条码格式,兼容不同快递公司的面单标准。测试阶段,在流水线满负荷运行场景验证,模块单包裹处理时间秒,识别成功率达,分拣错误率低,提升物流分拣效率。 定制 FPGA 的智能照明节能控制系统,根据环境光自动调光。赛灵思FPGA定制项目学习板

FPGA定制项目之医疗康复设备运动控制模块开发某医疗仪器公司需定制FPGA康复设备运动控制模块,用于下肢康复机器人,要求控制机械关节实现屈伸、旋转动作,动作角度范围0-120°,角度控制误差小于1°,且支持力度调节。项目团队选用AlteraArria10系列FPGA,其精细运动控制与安全保护能力符合医疗康复需求。FPGA接收康复师设定的运动参数,通过轨迹规划算法生成关节运动指令,控制伺服电机运转,同时通过力矩传感器监测运动力度,超出安全范围时自动减速。硬件设计加入紧急停止电路;软件层面支持多种康复模式预设。测试中,模块关节角度控制误差°,力度调节精度±,紧急停止响应时间小于200ms,可辅助患者进行下肢康复训练,满足医疗康复设备使用要求。 赛灵思FPGA定制项目学习板卫星通信地面站的 FPGA 定制,保障数据稳定高效传输。

FPGA定制项目之农业物联网土壤养分检测模块开发某农业科技公司需定制FPGA土壤养分检测模块,用于智慧农业大棚,要求检测土壤氮、磷、钾含量,检测误差小于10%,检测周期小于5分钟。项目组选用低功耗的LatticeMachXO3系列FPGA,搭配电化学传感器。FPGA控制传感器采集土壤样本信号,通过信号放大与模数转换将模拟信号转为数字量,再经校准算法计算养分含量,将结果上传至大棚管理系统。硬件设计采用防水封装适配田间环境,软件层面加入温度补偿功能,消除环境温度对检测结果的影响。测试阶段,在不同土壤类型验证,模块检测误差平均8%,检测周期4分钟,可辅助农户精细施肥。

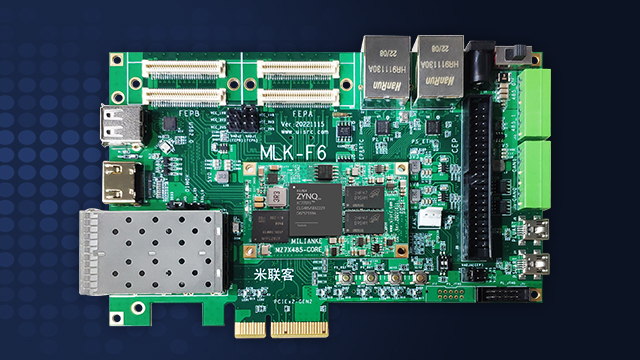

雷达信号处理FPGA定制开发低空监视雷达信号处理FPGA定制项目需实现目标探测距离10km,方位分辨率1度。项目前期进行详细性能需求分析,明确需支持脉冲压缩、动目标检测等信号处理算法。硬件选型采用XilinxUltraScale+系列FPGA,其丰富的DSP资源可满足大量乘加运算需求,高速ADC/DAC芯片实现信号收发。设计过程中采用迭代式方法,先完成基础信号处理模块,再根据外场测试数据优化算法参数。综合优化时重点提升脉冲压缩模块的运算效率,通过资源复用降低逻辑单元占用。时序仿真阶段加载实际雷达回波数据,验证目标检测算法的准确性。板级测试时通过示波器监测中频信号,解决了相位噪声导致的探测精度下降问题,实现目标跟踪更新率10Hz,满足低空安防监控需求。 FPGA 驱动的多通道数据采集卡,同时采集多路数据。

FPGA定制项目之海洋环境监测数据采集模块开发某海洋科研机构需定制FPGA海洋环境监测模块,用于近海海域监测,要求采集水温、盐度、海流速度3项数据,采样间隔1小时,能承受水下50米压力,且支持无线数据传输。项目团队对比后选用MicrochipPolarFire系列FPGA,其耐水压特性与低功耗设计适配海洋场景。开发中,FPGA通过水下传感器采集环境数据,先对模拟信号进行抗干扰处理,再经ADC转换为数字量,通过低功耗无线模块将数据上传至浮标接收站。硬件设计采用防水密封外壳,加入压力补偿结构;软件层面设置数据缓存功能,避免传输中断导致数据丢失。测试阶段,在近海区域部署模块,水温检测误差±℃,盐度检测误差±‰,海流速度检测误差±,连续水下工作30天无故障,满足海洋科研监测需求。 新能源发电监控的 FPGA 定制,保障发电设备稳定运行。安路开发板FPGA定制项目工程师

FPGA 定制助力 5G 基站优化信号处理,保障高速稳定通信。赛灵思FPGA定制项目学习板

通信基站信号处理FPGA定制项目某5G通信基站信号处理模块定制项目中,需求是实现10Gbps以上的高速信号解调与滤波。项目团队采用自顶向下设计方法论,先完成系统架构规划,将信号处理流程拆解为同步、解调、均衡等子模块。硬件选型上选用XilinxZynqUltraScale+系列FPGA,其集成的硬核处理器可负责配置管理,可编程逻辑资源实现并行信号处理。开发阶段通过Vivado工具链进行RTL编码与综合优化,针对滤波器模块采用流水线设计,将关键路径延迟缩短至,满足300MHz时钟需求。测试阶段运用ModelSim构建复杂测试激励,结合ChipScope在线调试,解决了时钟域交叉导致的信号抖动问题,终实现误码率低于1e-9的性能指标,适配多频段基站部署场景。 赛灵思FPGA定制项目学习板