晶体振荡器作为电子设备中不可或缺的主要时序元件,其工作原理建立在石英晶体独特的压电效应之上。当石英晶体受到交变电场作用时,会产生周期性的机械振动,而这种机械振动又会反过来生成交变电场,形成稳定的振荡回路。相较于其他类型的振荡器(如 RC 振荡器、LC 振荡器),晶体振荡器凭借石英晶体极高的机械稳定性,能够实现高频段下的精确振荡,频率稳定度通常可达 ±10ppm 至 ±0.1ppm 级别,远优于 RC 或 LC 振荡器。在实际应用中,这种精确的频率基准成为通信、导航、测量等领域的技术基石:在通信系统中,它为信号调制与解调提供稳定的载波频率,保障数据传输的准确性;在卫星导航设备(如 GPS、北斗终端)中,它为定位计算提供高精度的时间基准,直接影响定位误差;在精密测量仪器(如示波器、信号发生器)中,它则决定了测量结果的分辨率与可信度。无论是消费电子中的智能手机、笔记本电脑,还是工业领域的自动化控制设备,晶体振荡器都在幕后承担着 “时间管理者” 的角色,确保各类电子元件按序协同工作。 可编程晶体振荡器凭借软件配置灵活性,大幅缩短产品开发周期,告别传统晶振长交货期。深圳XDL晶体振荡器销售

老化率是衡量振荡器长期运行性能的重要指标,石英晶体振荡器具备极低的老化率,长期使用过程中频率漂移量小,能够明显延长设备的校准周期与使用寿命。在精密电子设备、工业控制、航空航天等领域,设备往往需要长时间连续运行,振荡器的老化会导致频率漂移逐渐增大,若漂移量超过允许范围,需对设备进行校准或更换器件,增加了维护成本与停机时间。石英晶体振荡器采用石英晶体材料,其物理化学性质稳定,长期使用过程中晶体的谐振特性变化极小,加之优化的封装与电路设计,进一步降低了器件的老化率。通常情况下,石英晶体振荡器的年老化率可控制在极低水平,长期使用后频率漂移量仍能保持在允许范围内,大幅延长了设备的校准周期,减少了维护成本,提升了设备的可靠性与使用寿命。TAITIEN泰艺晶体振荡器厂家TXC 晶技晶体振荡器采用 SMD 封焊工艺,-40℃~+85℃宽温稳定,20 年频率漂移只 ±4.6ppm。

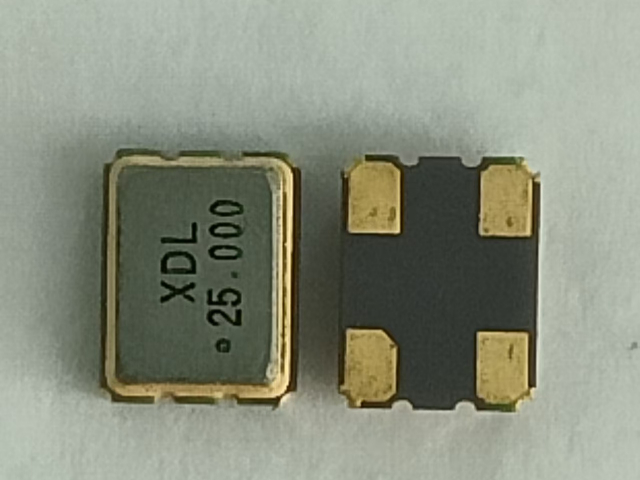

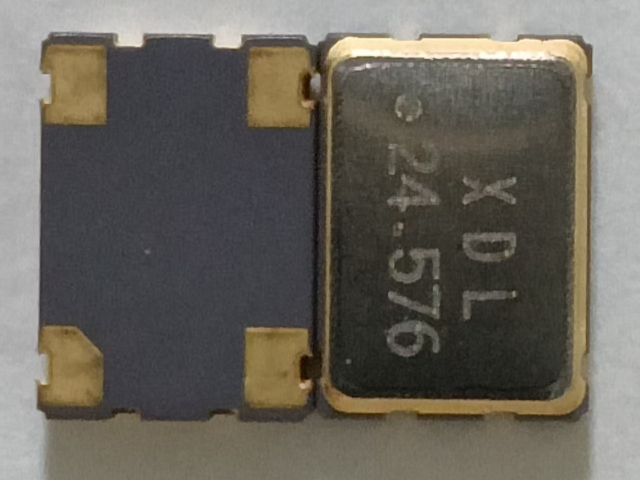

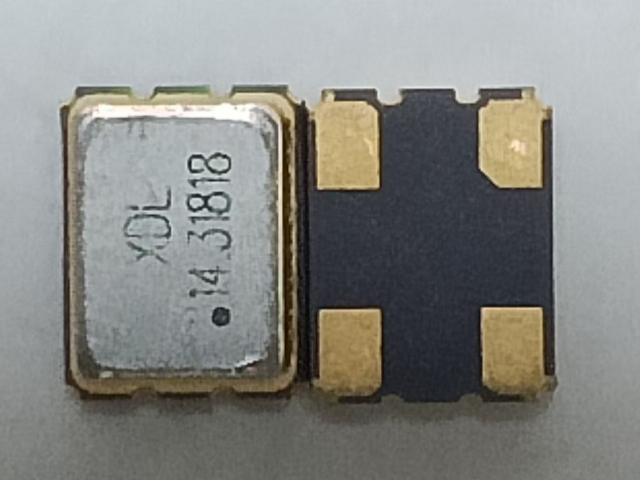

宽电压适配是SMD贴片晶体振荡器的重要特性之一,其能够兼容3.3V/5V等多种供电系统,有效降低了电路设计的复杂度与成本。在现代电子产品设计中,不同功能模块往往采用不同的供电电压,若振荡器无法适配多种电压,则需要额外增加电压转换电路,不仅增加了电路设计难度,还会导致设备体积增大、功耗上升。宽电压适配的SMD贴片晶体振荡器通过优化内部电路设计,采用宽电压范围的元器件与稳压技术,可在不同供电电压下稳定输出频率信号,无需额外配置电压转换模块。这一特性不仅简化了PCB板的电路设计,减少了元器件数量,降低了设计与制造成本,还提升了电路的可靠性,减少了因电压转换环节导致的故障风险,适配于各类消费电子、工业控制、物联网设备等不同电压需求的场景。

压控晶体振荡器是一种输出频率可由外部施加的控制电压(Vc)进行小范围调节的晶体振荡器。其关键技术是在振荡回路中引入了一个电压控制的可变电抗元件,通常是变容二极管。当外部控制电压改变时,变容二极管的结电容会随之线性变化,从而微调整个振荡回路的负载电容,实现对输出频率的牵引。这种“电调”特性使得VCXO成为闭环控制系统中不可或缺的部件,尤其是在锁相环(PLL)电路中。在PLL中,VCXO作为压控振荡器(VCO),其输出频率与一个高稳定的参考频率在鉴相器中进行比较,产生的相位误差电压经过滤波后,正好作为VCXO的控制电压,驱动其输出频率始终锁定在参考频率上,并能跟踪参考频率的相位变化。这一特性被广泛应用于频率合成、时钟恢复、同步信号生成以及消除系统中不同时钟域之间的静态相位误差等领域,是实现动态频率与相位校准的关键元件。插件晶体振荡器采用插装式结构,适配工业设备传统电路布局,安装便捷且抗干扰性强。

频率稳定度是高精度测量仪器的主要需求,高频晶体振荡器凭借±10ppm以内的超高频率稳定度,成为此类设备的优先频率基准器件。在精密电子测量、计量检测、医疗仪器等领域,测量结果的准确性直接依赖于频率信号的稳定性,频率漂移过大会导致测量误差增大,无法满足高精度测量要求。高频晶体振荡器通过采用高精度石英晶体谐振器、优化的振荡电路设计以及严格的温度控制措施,有效降低了温度变化、电源波动以及电磁干扰对频率稳定性的影响。其频率稳定度可精细控制在±10ppm以内,部分产品甚至可达更高精度级别,能够为高精度测量仪器提供恒定的频率参考,确保测量数据的准确性与可靠性,为科研实验、工业检测、医疗诊断等领域的精细化发展提供有力支撑。贴片有源晶体振荡器涵盖 1612~7050 多尺寸选项,满足消费电子与工业设备差异化需求。深圳温补晶体振荡器供应商家

插件晶体振荡器机械结构坚固,能耐受工业环境中的持续振动与电磁干扰。深圳XDL晶体振荡器销售

有源晶体振荡器(时钟模块)的主要优势之一在于其内部集成的输出缓冲级/驱动器,这赋予了它强大的信号驱动能力,从而从根本上保障了系统时钟的完整性(Signal Integrity)。在高速、高复杂度的数字系统中,时钟信号需要传输到多个负载(如多个FPGA、CPU、ASIC),传输路径上的分布电容、传输线效应以及负载的输入电容会严重劣化信号质量,导致边沿变缓、产生振铃或过冲。如果使用无源晶体,其输出信号微弱,无法直接驱动长走线和多负载,必须额外添加缓冲器,增加了设计和布板的复杂性。而有源晶振的输出级是专门设计的,能够提供低阻抗输出,通常具备数十毫安的量级驱动电流,能够快速地对负载电容和传输线电容进行充放电,从而产生边沿陡峭(快速上升/下降时间)、波形规整的时钟信号。这不仅减少了信号抖动(Jitter),也明显增强了抗干扰能力,确保在接收端能够获得明确、稳定的逻辑电平。对于DDR内存、高速串行总线(如PCIe、SATA)等对时序要求极其苛刻的应用,一个有源晶振提供的“干净”时钟是系统稳定运行、达到理论性能指标的基础保障。深圳XDL晶体振荡器销售