- 品牌

- FCom富士晶振

- 型号

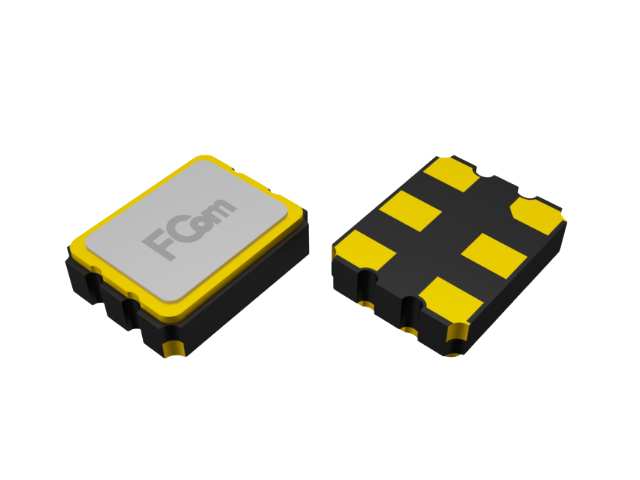

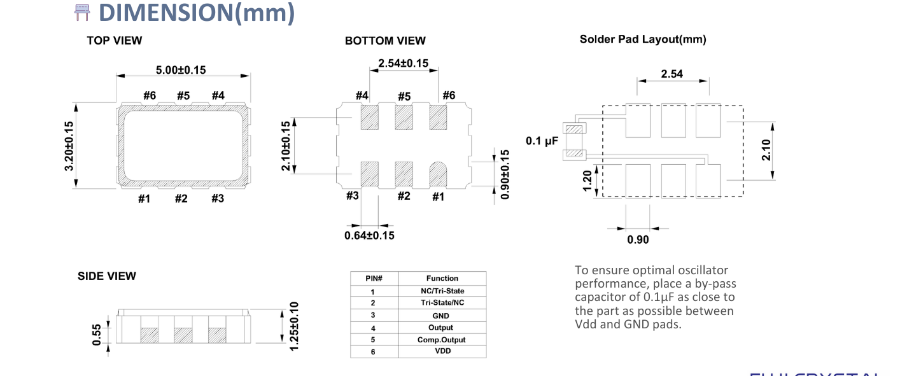

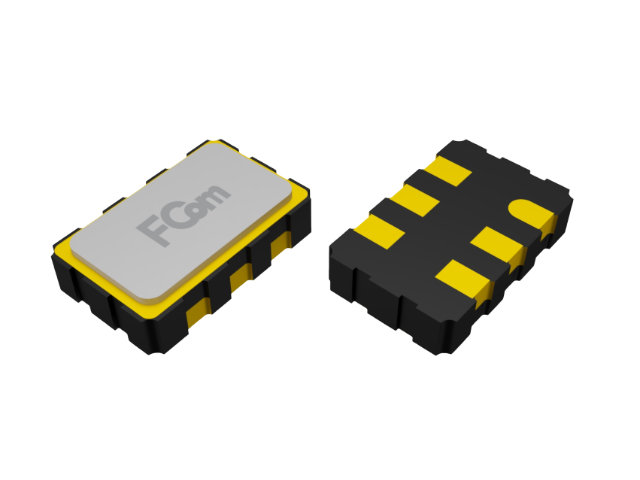

- FCO-L-PG

- 系列

- FCO-L-PG

- 类型

- MHz晶体

- 频率范围

- 10 MHz ~ 220 MHz

- 工作电压

- 1.8V / 2.5V / 3.3V 可选

- 温度频差

- ±25ppm / ±50ppm(出厂可选)

- 工作温度

- –40°C ~ +105°C

- 相位抖动

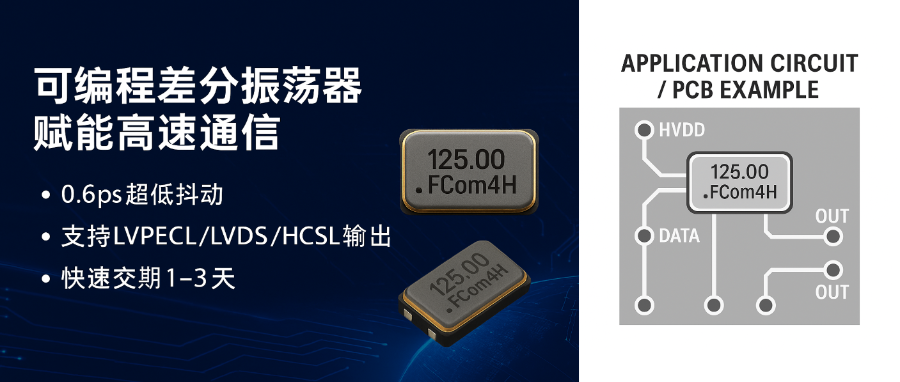

- 0.2 ~ 0.6ps RMS(12kHz~20MHz)

AI服务器中的低功耗多时钟域管理 AI服务器通常集成多个计算加速卡(GPU、TPU、FPGA)、高速内存(HBM/DDR5)、高速IO接口(PCIe Gen5、CXL、NVLink)、大容量本地存储及高速网络通道。系统运行过程中存在多个异步时钟域,传统单一时钟方案难以满足所有模块同步要求。FCom富士晶振可编程差分振荡器,凭借其灵活配置、低抖动、多接口支持,成为AI服务器主板中多时钟域协同管理的关键。 FCom差分振荡器可通过OTP或配置工具预设多个频点,并在电路中配置三态控制,动态切换参考频率。例如: - GPU加速卡使用100MHz HCSL - CXL互联使用133.33MHz LVDS - 高速网卡使用156.25MHz PECL - 存储控制器使用200MHz LVDS 每路接口均可控制启用状态,实现节能模式下时钟通道屏蔽。其低至4~5mA典型功耗表现,在AI服务器高能耗密度背景下,突出降低整板温升。可编程差分振荡器适用于低功耗+高频率应用需求。高频可编程差分振荡器厂家报价

可编程差分振荡器

加密加速器芯片中的高精度参考时钟应用 在金融安全平台、区块链计算设备、国密算法卡中,加密加速器芯片负责大量数据包的加解开操作,对参考时钟的稳定性与抖动水平高度敏感。FCom富士晶振可编程差分振荡器支持定制频率与接口输出,满足对AES、SM系列算法高速处理过程中的严苛抖动约束。 该系列支持50MHz、100MHz、125MHz等频点,输出格式支持HCSL与LVDS,典型抖动控制在0.05ps以内,频率稳定度±10ppm以内,可用于作为AES/SM4加速器、RSA解码引擎与高速通信安全接口的基准时钟。 产品支持静态频率编程与多通道输出配置,可根据加密平台部署场景灵活设定不同区域模块参考频率,提高加密通道互联的一致性与安全性。 目前该器件已被各个方面集成于金融安全加密卡、国产化服务器国密主板、安全芯片开发平台与区块链矿机加速模块中。高频可编程差分振荡器厂家报价可编程差分振荡器提升下一代网络架构频率管控效率。

服务器主板设计中的灵活频点调配机制 现代服务器主板集成处理器、存储、网络、扩展总线、硬件加速器等多种模块,每种子系统所需参考时钟频点及输出类型均不相同。传统设计需要多个不同频率的晶振搭配缓冲器与MUX,布线复杂、功耗高、EMI风险大。FCom富士晶振推出的可编程差分振荡器可简化服务器主板时钟系统设计,实现灵活频点调配与结构一体化。 该系列产品支持常见主板频点如25MHz、48MHz、100MHz、125MHz、156.25MHz、200MHz,可分别配置输出给以太网PHY、PCIe控制器、DDR5时钟分布芯片、BMC管理芯片等模块。通过配置脚与I²C控制,可实现动态频率切换、接口格式切换与时钟启停管理。 FCom差分振荡器支持双输出、三态控制与电平自动适配机制,使得其在主板上可替代多个不同晶振,提升主板模块化程度与兼容能力。其功耗低于6mA,适合大型服务器24/7高负载运行场景。

该振荡器的频率稳定度控制在±10ppm以内,在极端温度环境下(-55~+125℃)仍可保持时钟精确输出。封装方面,FCom提供7050、5032等多规格工业级气密封封装,满足雷达系统对抗震、抗干扰、防潮的使用需求。特别适用于相控阵雷达、海事雷达、机场航迹管理系统与前沿气象探测设备等场景。 此外,FCom产品支持双频冗余备份与软切换机制,在主通道失效时自动调用备用时钟路径,进一步增强了雷达信号链的系统稳定性。通过GUI配置工具,工程人员可快速在开发阶段切换频点、修改接口逻辑,从而降低设计风险与调试成本。多通道通信系统依赖可编程差分振荡器保持时序一致。

器件具备抖动控制在0.05ps~0.1ps范围,突出提升图像同步效果,消除帧延迟和马赛克问题。 通过多频点编程能力,用户可统一采用一颗器件输出多个视频接口时钟,避免板上使用多组晶振并产生交叉干扰。其宽压输入支持1.8V至3.3V平台,兼容各类图像处理芯片I/O标准。 此外,产品具备三态功能、OE控制与输出屏蔽逻辑,可在设备未启用状态下关闭时钟输出以减少系统功耗。FCom产品已部署于电视台演播主控、8K信号矩阵、视频融合服务器、指挥中心显示控制平台中,是高清多通道系统的稳定时钟支撑基础。可编程差分振荡器为高速信号链提供精确时基。FCO-3L-PG可编程差分振荡器电话

可编程差分振荡器应用于高速数据中心主板时钟设计。高频可编程差分振荡器厂家报价

高速SerDes链路中的Jitter抑制解决方案 SerDes(串并转换器)作为现代高速通信链路的关键模块,其性能直接受参考时钟信号抖动与相位稳定性的影响。尤其在PCIe Gen4/Gen5、10G/25G/56G Ethernet、USB4、SATA等高速链路中,SerDes对参考时钟的RMS抖动容差通常在0.15ps以下。FCom富士晶振推出的可编程差分振荡器,正是为满足高速SerDes链路严苛抖动规范而设计。 该系列产品采用低噪声PLL与高线性VCXO内核设计,有效抑制输出Jitter,实际测试中可提供低至0.05ps RMS的优异表现,支持多种差分输出标准(LVDS、LVPECL、HCSL),同时具备±25ppm/±50ppm频稳可选,适配不同信号敏感度需求。高频可编程差分振荡器厂家报价

- 多输出可编程差分振荡器有哪些 2025-12-23

- 有什么可编程差分振荡器商家 2025-12-22

- 可编程可编程差分振荡器怎么样 2025-12-21

- 高性能可编程差分振荡器怎么样 2025-12-21

- FCO-3L-PG可编程差分振荡器电话 2025-12-21

- 高频可编程差分振荡器厂家报价 2025-12-21

- FCO-3L-PG可编程差分振荡器产品介绍 2025-12-20

- 高性能可编程差分振荡器订做价格 2025-12-20

- 可编程差分振荡器常见问题 2025-12-20

- FC5LPG可编程差分振荡器怎么样 2025-12-20

- FCO-5L-PG可编程差分振荡器技术指导 2025-12-19

- 新型可编程差分振荡器联系方式 2025-12-19