中清航科推出SI/PI协同仿真平台,集成电磁场-热力多物理场分析。在高速SerDes接口设计中,通过优化封装布线减少35%串扰,使112GPAM4信号眼图高度提升50%。该服务已帮助客户缩短60%设计验证周期。中清航科自主开发的AMB活性金属钎焊基板,热导率达180W/mK。结合银烧结工艺的IGBT模块,热循环寿命达5万次以上。在光伏逆变器应用中,另功率循环能力提升3倍,助力客户产品质保期延长至10年。通过整合CP测试与封装产线,中清航科实现KGD(已知良品)全流程管控。在MCU量产中采用动态测试分Bin策略,使FT良率提升至99.85%。其汽车电子测试仓温度范围覆盖-65℃~175℃,支持功能安全诊断。穿戴设备芯片需轻薄,中清航科柔性封装,适配人体运动场景需求。上海半导体封装测试

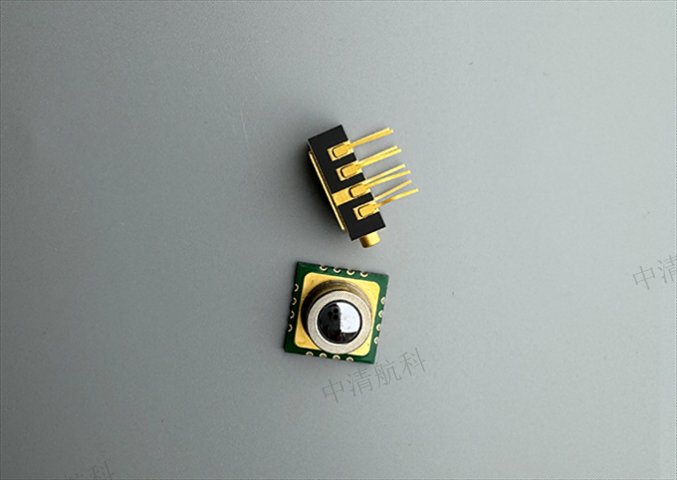

常见芯片封装类型-DIP:DIP即双列直插式封装,是较为早期且常见的封装形式。它的绝大多数中小规模集成电路芯片采用这种形式,引脚数一般不超过100个。采用DIP封装的芯片有两排引脚,可插入具有DIP结构的芯片插座,也能直接焊接在有对应焊孔的电路板上。其优点是适合PCB上穿孔焊接,操作方便;缺点是封装面积与芯片面积比值大,体积较大。中清航科在DIP封装业务上技术成熟,能以高效、稳定的生产流程,为对成本控制有要求且对芯片体积无严苛限制的客户,提供质优的DIP封装产品。上海扇出型晶圆级封装中清航科芯片封装创新,以客户需求为导向,定制化解决行业痛点难题。

面对量子比特超导封装难题,中清航科开发蓝宝石基板微波谐振腔技术。通过超导铝薄膜微加工,实现5GHz谐振频率下Q值>100万,比特相干时间提升至200μs。该方案已用于12量子比特模块封装,退相干率降低40%,为量子计算机提供稳定基础。针对AI边缘计算需求,中清航科推出近存计算3D封装。将RRAM存算芯片与逻辑单元垂直集成,互连延迟降至0.1ps/mm。实测显示ResNet18推理能效达35TOPS/W,较传统方案提升8倍,满足端侧设备10mW功耗要求。

中清航科深紫外LED封装攻克出光效率瓶颈。采用氮化铝陶瓷基板搭配高反射镜面腔体,使280nmUVC光电转换效率达12%。在杀菌模组应用中,光功率密度提升至80mW/cm²,寿命突破10,000小时。基于MEMS压电薄膜异质集成技术,中清航科实现声学传感器免ASIC封装。直接输出数字信号的压电微桥结构,使麦克风信噪比达74dB。尺寸缩小至1.2×0.8mm²,助力TWS耳机减重30%。中清航科太赫兹频段封装突破300GHz屏障。采用石英波导过渡结构,在0.34THz频点插损<3dB。其天线封装(AiP)方案使安检成像分辨率达2mm,已用于人体安检仪量产。芯片封装成本压力大,中清航科材料替代方案,在降本同时保性能。

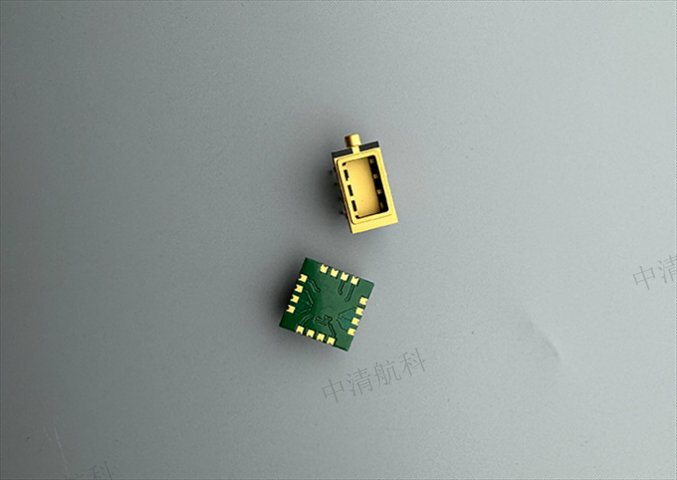

针对MicroLED巨量转移,中航清科开发激光释放转印技术。通过动态能量控制实现99.99%转移良率,支持每小时500万颗芯片贴装。AR眼镜像素密度突破5000PPI。基于忆阻器交叉阵列,中清航科实现类脑芯片3D封装。128×128阵列集成于1mm²面积,突触操作功耗<10pJ。脉冲神经网络识别准确率超96%。中清航科超导芯片低温封装解决热应力难题。采用因瓦合金基板,在4K温区热失配<5ppm/K。量子比特频率漂移控制在±0.1GHz,提升多比特纠缠保真度。中清航科芯片封装技术,支持三维堆叠,突破平面集成的性能天花板。qfn64封装

中清航科芯片封装创新,支持多芯片异构集成,突破单一芯片性能局限。上海半导体封装测试

芯片封装的散热设计:随着芯片集成度不断提高,功耗随之增加,散热问题愈发突出。良好的散热设计能确保芯片在正常温度范围内运行,避免因过热导致性能下降甚至损坏。中清航科在芯片封装过程中,高度重视散热设计,通过优化封装结构、选用高导热材料、增加散热鳍片等方式,有效提升封装产品的散热性能。针对高功耗芯片,公司还会采用先进的液冷散热封装技术,为客户解决散热难题,保障芯片长期稳定运行,尤其在数据中心、高性能计算等领域发挥重要作用。上海半导体封装测试